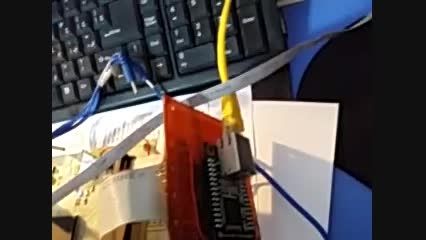

پیاده سازی سخت افزاری PID کنترلر مالتی پلکس شده در FPGA

389 بازدید

389 بازدید

هدف این پروژه که بخشی از پایان نامه کارشناسی ارشد رشته هوش مصنوعی می باشد، پیاده سازی سخت افزاری یک کنترل کننده کلاسیک مالتی پلکس شده بر روی FPGA می باشد. ویژگی این پیاده سازی استفاده از یک کنترل کننده فوق سریع برای کنترل همزمان 4 موتور حرکتی یک روبات است. بدین صورت که در هر لحظه از زمان وضعیت سرعت و گشتاور یک موتور چک می شود.

https://ir.linkedin.com/in/kiamnasri

اولین نفری باشید که برای این ویدیو دیدگاه ارسال میکنید